# 令和5年度 電子回路学 後期定期試験問題 (01/29/24)

- 25点 25点

- 氏名 HI3番号

点 No.1 得点

HI1302

$R_{\,2}$

$R_{\,3}$

図 4 FET のバイアス回路

$250\,\Omega$

$750\,\Omega$

$V_{

m DD}$

12 V

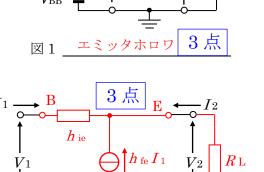

- 1. 図1の回路について、以下の問に答えよ.

- (1) 回路名を下線部に書き, 図 2 に hie と hfe を用いた等価 回路を描け.

- (2) 入力インピーダンス Ri と電圧利得 Av を導出せよ.

### 図より

$$V_1 = h_{ie} I_1 + (1 + h_{fe}) I_1 R_L$$

(1)

従って、入力インピーダンス Riは

$$Ri = \frac{V_1}{I_1}$$

$= h_{ie} + (1 + h_{fe}) R_{L}$

4 点

(2)

となる. 次に,  $V_2$ は

$$V_2 = (1 + h_{\rm fe}) I_1 R_{\rm L}$$

(3)

で表されるので、電圧利得 A v は

$$A v = \frac{V_2}{V_1}$$

$$= \frac{(1+h_{fe})R_L}{h_{ie} + (1+h_{fe})R_L} = 1$$

(4)

となる.

図 2 hie と hfe を用いた等価回路

- 2. 図3の回路名を下線部に書き、以下の問いに答えよ. 但し、電 源は  $V_{DD}=5V$ ,  $V_{SS}=0V$  とする.

- (1)  $V_{GS1}$  と  $V_{GS2}$  を式で表し、 $V_{1}=5$ V のときと 0V のときの値を それぞれ求めよ.

#### $V_{\rm GS1}$ :

図より、 $V_{GS1} = V_1 - V_{DD} = V_1 - 5$  (V)

$V_1 = 5V$  のとき:  $V_{GS1} = 5-5=0$  (V)

4 点

$V_1 = 0V \cap 2 \approx V_{GS1} = 0-5=-5 \text{ (V)}$

$V_{\rm GS1}$  $\square$ Q<sub>1</sub> 3 点 図3 CMOS インバータ

#### $V_{\rm GS2}$ :

同様に、 $V_{GS2} = V_1 - V_{SS} = V_1$  (V)

$V_1=5V \circ 2 : V_{GS2}=5 (V)$

$V_1=0V \cap \xi$ :  $V_{GS2}=0 (V)$

4点

(2) 表 1 の空欄を埋めよ. 但し, Q1, Q2 との欄は オンなら○でオフなら×で記入せよ.

4 点

| 表 1 図 3 の動作表 |              |              |                |                |       |  |  |  |

|--------------|--------------|--------------|----------------|----------------|-------|--|--|--|

| $V_1$        | $V_{ m GS1}$ | $V_{ m GS2}$ | $\mathbf{Q}_1$ | $\mathbf{Q}_2$ | $V_2$ |  |  |  |

| 5V           | 0V           | 5V           | ×              | 0              | 0V    |  |  |  |

| 0V           | -5V          | 0V           | 0              | ×              | 5V    |  |  |  |

$4k\Omega$

- 3. 図4の回路について、以下の問いに答えよ.

- (1) 図の FET は何チャネルの何 FET か.

### n チャネル接合形 FET

3 点

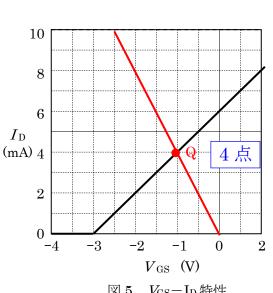

(2) 図の V<sub>GS</sub> を V<sub>DD</sub>, I<sub>D</sub>, および抵抗の記号を用いて表せ(各 素子値を代入した式も求める).

図より、ゲートには電流が流れないので

$V_{GS} = -R_3 I_D$

Inを mA で表し、各素子値を代入すると

$V_{GS} = -0.25I_{D}$

4点

となる.

(参考) Љを求めると

$I_D = -4V_{GS}$  [mA]

(3) 図 5 は Vos-In 特性である. (2) で得られた式のグ ラフを図中に記入し,動作点Qを書き込め.また, 無信号時の  $V_{GS}$  と  $I_D$  を求めよ.

> $V_{\rm GS} =$ -1 V

4 mA  $I_{\rm D} =$

3 点

図 5 V<sub>GS</sub>-I<sub>D</sub>特性

## 令和5年度 電子回路学 後期定期試験問題 (01/29/24)

25点 25点

HI3番号 氏名

No. 2

HI1302

1 3 伊万\_\_\_\_\_\_ 八名\_\_\_\_

- 4. 図6について、以下の問いに答えよ.

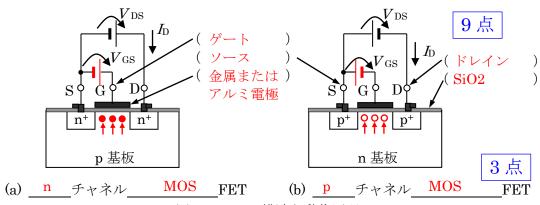

- (1) 下線部に FET の名称を書き、図中の括弧内に端子等の名称を記入せよ.

図 6 FET の構造と動作原理

(2) 同図(a) 中に h を流すように  $V_{GS}$  を記入して,チャネル内に電子を $\bullet$ で正孔を $\circ$ で,その動きを矢印で記入し,動作を説明して h が流れる理由を述べよ. 3 点

ゲートGの下面にはn チャネルが作られていないので、 $V_{CS}>2\sim3V$ 程度の正電圧にするとゲートの下面に電子が集まり、この電子がチャネルを形成して $I_D$ が流れる。

(3) 同図(b) 中に  $f_0$  を流すように  $f_0$  を記入して, チャネル内に電子を $f_0$  で正孔を $f_0$  で正孔をを決印で記入し, 動作を説明して  $f_0$  が流れる理由を述べよ.

ゲートGの下面にはpチャネルが作られていないので、 $V_{GS}<-2\sim-3V$ 程度の負電圧にするとゲートの下面に正孔が集まり、この正孔がチャネルを形成してが $\Delta$ が流れる.

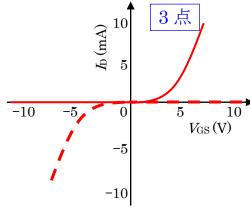

- (4) 図 7 に図 6(a)と(b)の  $V_{GS}$ - $I_D$ 特性を描け、但し、図 6(a)の特性は実線で、図 6(b)の特性は破線で描け、

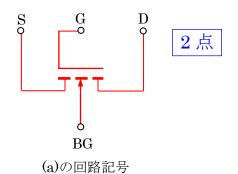

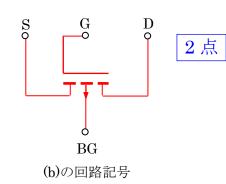

- (5) 図 6(a)と(b)の回路記号をそれぞれ図 8 の(a)と(b)に描け.

図7 VGS-In特性

図8 図6の回路記号

(1) 下線部に回路名を記入せよ.(2) しきい値電圧 V<sub>T</sub>を求めよ.

$V_T = \frac{V_{DD} + V_{SS}}{2} = 2.5 \text{ V}$

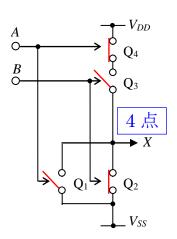

5. 図9について、以下の問いに答えよ.

2点

(3) 下の素子名を下線部に書け.

3点

Q1: <u>n</u> チャネル <u>MOSFET</u>

Q3: <u>p</u>チャネル MOSFET

(4)  $Q_5 \sim Q_8$  の動作を説明せよ.

4 点

$Q_3$  X  $Q_6$   $Q_8$   $Q_7$   $Q_7$   $Q_7$   $Q_7$   $Q_7$   $Q_8$   $Q_8$

+  $V_{DD}=5V$

$Q_4$

5 点

$Q_5$ と  $Q_6$ ,  $Q_7$ と  $Q_8$ とでインバータを構成し, Y=X と信号は同じになるが, 出力 Yは X の出力

より多くの電流を流せるバッファーの働きをする.

(5) 入力 A =0V, B =5V とした場合で,  $Q_1 \sim Q_4$  のスイッチ状態を図 10 に描いて途中の電圧 Xを求めよ.

電圧

$$X = 0$$

V

(6) 表 1 の空欄を埋めよ. 但し、簡単のため、0V は"0"で、5V は"1"で表し、スイッチ状態はオンで $\bigcirc$ 、オフは $\times$ で表す.

表9 図0の動作表

| 衣 2 因 9 0 期 日 衣 |   |                |                |                |                | 0 11 | 15             |                  |                |                |    |

|-----------------|---|----------------|----------------|----------------|----------------|------|----------------|------------------|----------------|----------------|----|

| 入               | 力 |                | スイッ            | チ状態            | ł              | 途中   | ``\            | スイッ              | チ状態            | 30%            | 出力 |

| A               | B | $\mathbf{Q}_1$ | $\mathbf{Q}_2$ | $\mathbf{Q}_3$ | $\mathbf{Q}_4$ | X    | $\mathbf{Q}_5$ | $\mathbf{Q}_{6}$ | $\mathbf{Q}_7$ | $\mathbf{Q}_8$ | Y  |

| 0               | 0 | ×              | ×              | 0              | 0              | 1    | 0              | ×                | X              | 0              | 1  |

| 0               | 1 | ×              | 0              | ×              | 0              | 0    | ×              | 0                | 0              | ×              | 0  |

| 1               | 0 | 0              | ×              | 0              | ×              | 0    | ×              | 0                | 0              | ×              | 0  |

| 1               | 1 | 0              | 0              | ×              | ×              | 0    | ×              | 0                | 0              | ×              | 0  |

図10スイッチで表した回路

(7) 入力A, Bと出力Yの関係を論理回路で描け.

## 令和5年度 電子回路学 後期定期試験は以下のような問題である.

(試験範囲 7章(pp. 112-116), 8章(pp. 131-148), CMOS(教科書にない). ★小テスト, 配布資料, およびノート) 出題者:大田

- 1. エミッタホロワ (負帰還増幅回路) の回路図を与えるので次の問に答える(p.112). ★★

- (1) 回路名を書く(エミッタホロワ,コレクタ接地増幅回路)(エミッタホロワ回路は不可).

- (2) トランジスタを  $h_{ie}$ と  $h_{fe}$ の等価回路で描く.

- (3) 各部の電圧 (電流) を求め、電圧 (電流) 増幅度と入 (出) カインピーダンス  $Z_i$  ( $Z_o$ ) を求める.

- 2. 電界効果トランジスタ (FET) の原理図を与えるので次の問に答える $(p.131\sim)$ .  $\star\star$

- (2) ゲート電圧 VGs で電子●や正孔oがどう動くかを描いて、電流が流れるか・流れないか を説明する.

- (3) FET の動作から伝達特性( $V_{GS}$   $-I_D$ 特性)を概略描ける.

- (4) FET の原理図を回路記号で描ける  $(n \cdot p f + r \cdot h)$ , 接合形・MOS 形かの判断).

- 3. FET のバイアス回路, 伝達特性 ( $V_{GS}$ - $I_D$ 特性), 出力特性 ( $V_{DS}$ - $I_D$ 特性) を与えるので次の問に答える(p.138)【トランジスタの場合と同様】.  $\star\star$

- (1) FET 名を書く (n チャネル, p チャネル) (接合形, MOS 形) FET.

- (2) 負荷線を求める回路を描き、負荷線 ( $V_{GS}$ や $I_D$ ) の式を求める.

- (3) 伝達特性 (VGS-AD特性) や出力特性 (VDS-AD特性) 上に負荷線と動作点を描く.

- (4) 動作点から, 無信号時の V<sub>GS</sub>, V<sub>DS</sub>, Lo を求める,

- (5) 動作点の移動から電圧増幅度を求める.

- (6) **FET** の等価回路を  $g_m$  と  $r_d$ で表し、各部の電圧(電流)を求め、増幅度や入(出)力インピーダンスを求める.

- 4. C-MOS 回路 (インバータ, NAND 回路, NOR 回路) を与えるので次の問に答える(教科書にない). ★★

- (1) 電源電源 ( $V_{DD}$ ,  $V_{SS}$ ) から、しきい値電圧  $V_T$  を求め、各 MOSFET の  $V_{GS}$  の式を求め、各 MOSFET スイッチのオン・オフを判断して、入力電圧と出力電圧の関係を求める.

- (2) 入力波形を与えるので、出力電圧波形を描く、

- (3) 入出力電圧の関係から、論理回路図(NOT, NAND, NOR)で描く.

- ★★各自、配布資料、★小テストをもう一度、何も見ずに解いてみること、★★

以上を何も見ずに全て解けるようになれば、90点以上は取れる問題を出す. 普段できないことは、試験でもできません! 必ず、各自解いてみること!